# INTENTO DESIGN, INNOVATION FOR ANALOG

### TECHNOLOGY BEHIND THE SOLUTIONS

June 2023 - Presentation under NDA

## **Intento Design Mission**

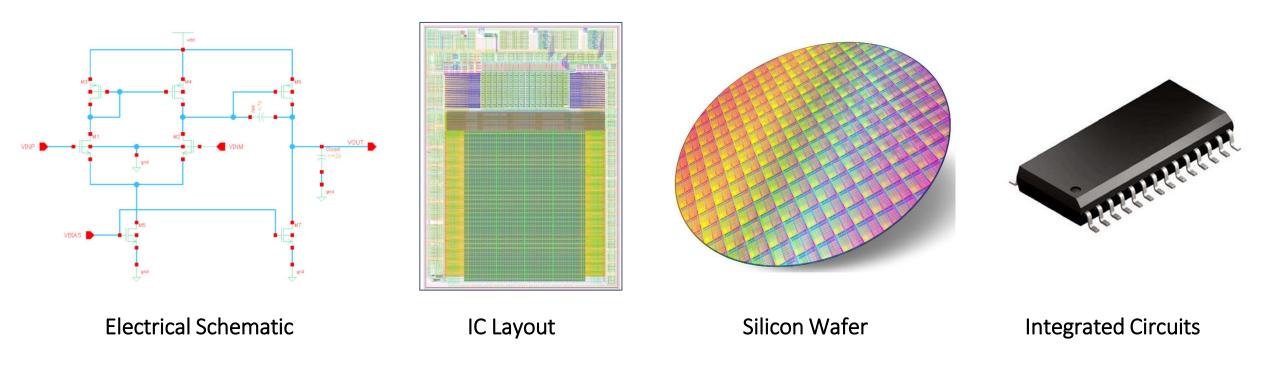

# We are a Software company developing Electronic Design Automation tools to design Semiconductor Analog Integrated Circuits

### Analog Design Challenges

### Our World is Analog

- Analog circuits are used for

- Power Management

- Battery Management

- Communication (transceiver)

- Audio

- Sensors

- Analog Designs are technology dependent

- They need to be redesigned for every process/foundries

- Analog design flow is still time consuming and laborious with drastic impact cost and time to market.

### We need innovation in EDA for Analog

- Analog Designers are becoming rare

- Hiring is tough

- Learning curve is long

- Demand for Analog is booming due to

- Electric vehicles, Battery based systems

- Modern SoC integrates more and more Analog blocks (Transceiver, DAC, PLL, Interfaces, ...)

- Getting an optimum design is costly

- Time, Human and hardware resources

- Analog Design must support a very large number of silicon technologies and foundries

- Design porting cost increasing particularly for advanced node

- First prototyping request is very costly

- Zero respin is the target

### Why do we need innovation in EDA for Analog IC ?

### Analog ICs are everywhere around us

- Mobile Phone:

- Battery Management and Charge

- Audio, Sensors

- Electric Vehicles:

- Key components for the Battery Management and Control impacting the range of the vehicle, the speed of charging

- IOT: Sensors, Interfaces,...

### Challenges of Analog Design

- Analog Designers are becoming rare

- Demand for Analog is booming

- Getting an **optimum design is costly**

- Analog Design must support a very large number of silicon technologies and foundries

- Need Efficient Automation in Analog Design

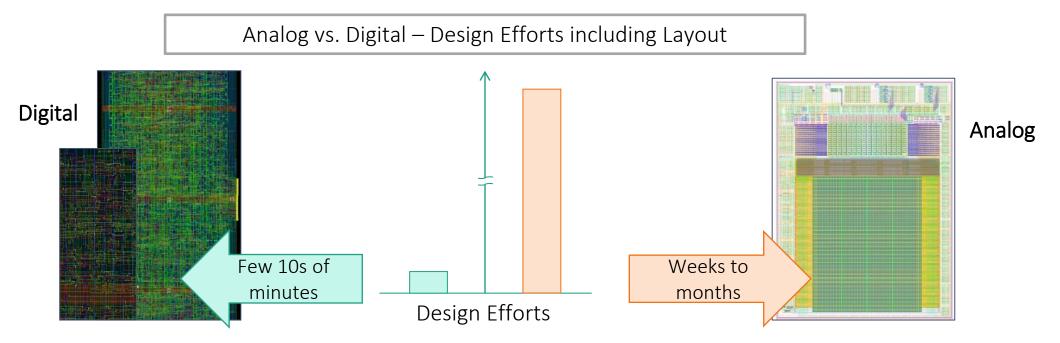

### Motivation to Automate Analog IC Design

- Business needs:

- Improve development cycle time

- Minimize design errors

- Reduce Costs

- Technical pains:

- Technologies have a strong impact on Analog

- Analog design still very "manual"

- Analog modeling is not mature

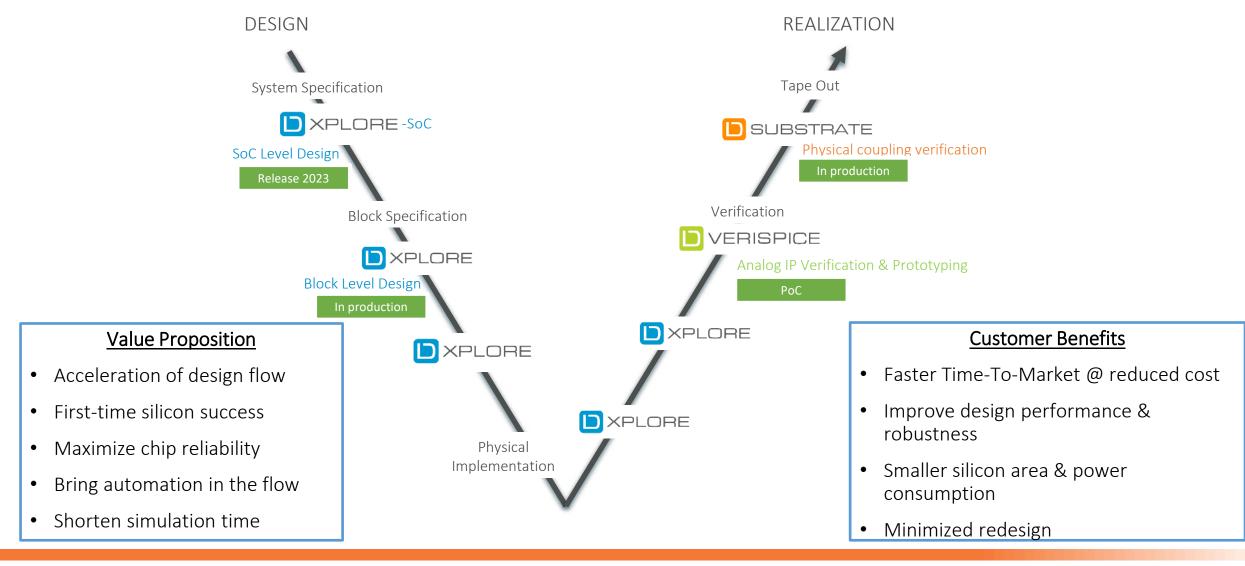

### Intento Design Solutions for Analog Design Flow

### Intento Design EDA solutions in Production

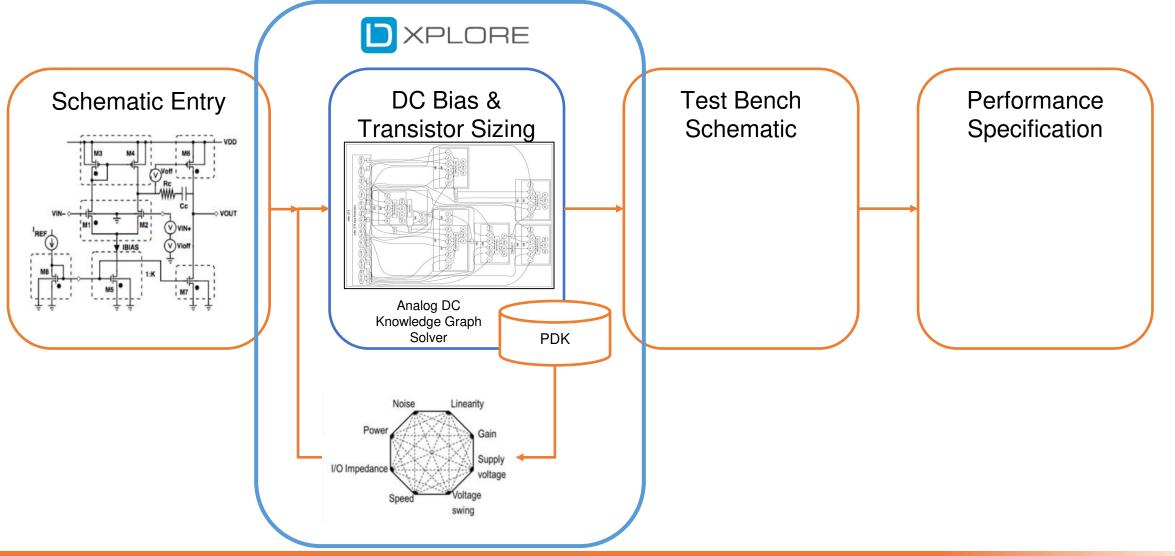

- ID-Xplore is a powerful and disruptive EDA tool that can significantly accelerate the design flow.

- Easy-to-use

- Fast and reliable design

- Full integration in design flow with Virtuoso Environment

- Foundry & technology agnostic

- ID-Substrate captures all types of substrate noise coupling and analyze possible substrate failure effects

- Unique on the market

- Save time and cost avoiding reworking

- Increase reliability

- Full integration in design flow with Virtuoso Environment

Already in Production with WW analog leaders like STMicroelectronics, AMS OSRAM and others

ID-Xplore<sup>™</sup>

#### Ultra Fast Design and Migration of Analog IP

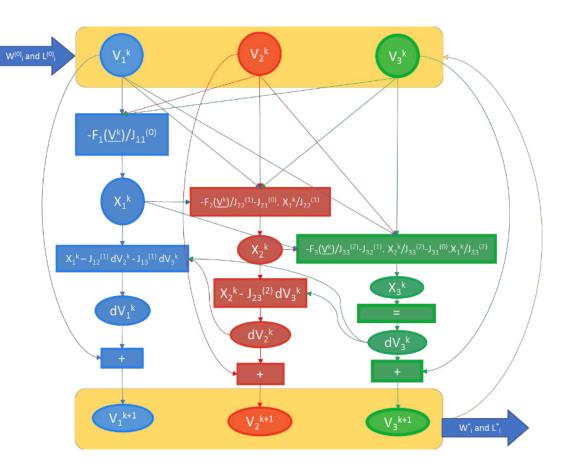

### Spice Simulators are based on Nonlinear DC Analysis

- 1. From **NR algorithm**:  $J^k \Delta v^k = -f(v^k)$

- 2. From LU Decomposition:  $J \equiv L U \equiv \begin{bmatrix} J_{11}^{(0)} & 0 & 0 & 0 \\ J_{21}^{(0)} & J_{22}^{(1)} & 0 & 0 \\ J_{31}^{(0)} & J_{32}^{(1)} & J_{33}^{(2)} & 0 \\ J_{41}^{(0)} & J_{42}^{(1)} & J_{43}^{(2)} & J_{44}^{(3)} \end{bmatrix} \begin{bmatrix} 1 & J_{12}^{(1)} & J_{13}^{(1)} & J_{14}^{(1)} \\ 0 & 1 & J_{23}^{(2)} & J_{24}^{(2)} \\ 0 & 0 & 1 & J_{34}^{(3)} \\ 0 & 0 & 0 & 1 \end{bmatrix}$

- 3. We get:  $L^k U^k \Delta v^k = -f(v^k)$

- 4. Substituting by  $\boldsymbol{x^k}$  :  $\boldsymbol{x^k} = \boldsymbol{U^k} \Delta \boldsymbol{v^k}$

- 5. We first solve the lower triangular matrix by Forward Substitution:  $L^k x^k = -f(v^k)$

- 6. Solve the upper triangular matrix by Back Substitution to get  $\Delta v : U^k \Delta v^k = x^k$

- 7. 7. Finally, we update current variables:  $v^{k+1} = v^k + \Delta v^k$

### Why Spice Simulations Are Limited in Speed ?

### SPICE computational model is complex Representation of Spice DC Simulation

- Matrix-based formulation

- Simultaneous Resolution in SPICE:

- Each iteration requires a large number of computations

- Jacobian computation becomes a major difficulty

# ID-Xplore Approach for Analog Design

Mimic Designer Method for Schematic Design, Migration and Simulation

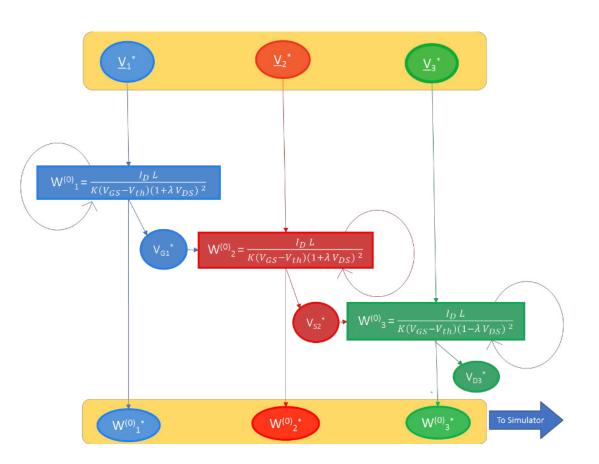

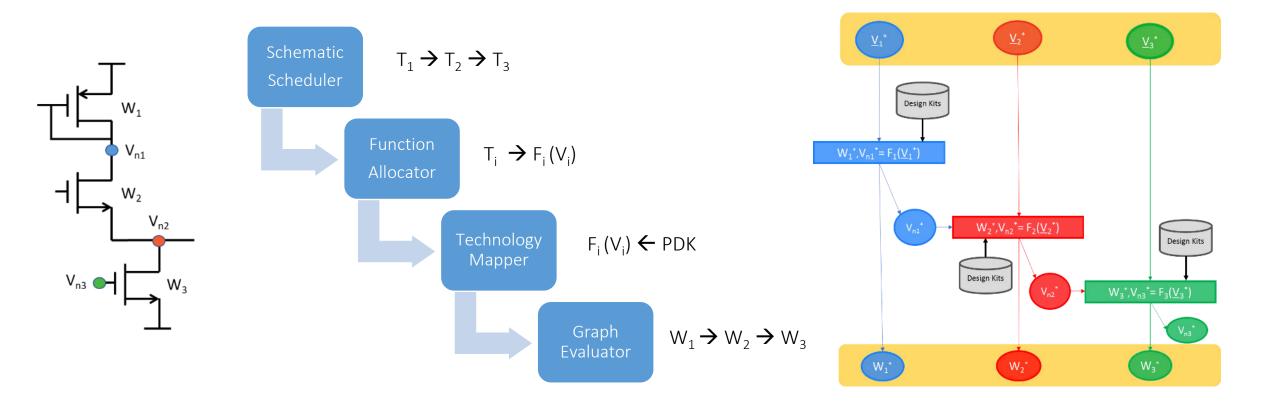

#### Computational model becomes very simple

- Structured Resolution

- No matrix-based formulation

- Each iteration requires only one computation

- Jacobian computation almost disappears

## ID-Xplore Approach for Analog Design:

Digitally EDA-Inspired, Constraint-Driven Design Methodology

#### Fast, Error-Free, Deterministic and Correct-by-Construction

Intento Design Confidential Information

Intento Design Confidential Information

Execution time in seconds

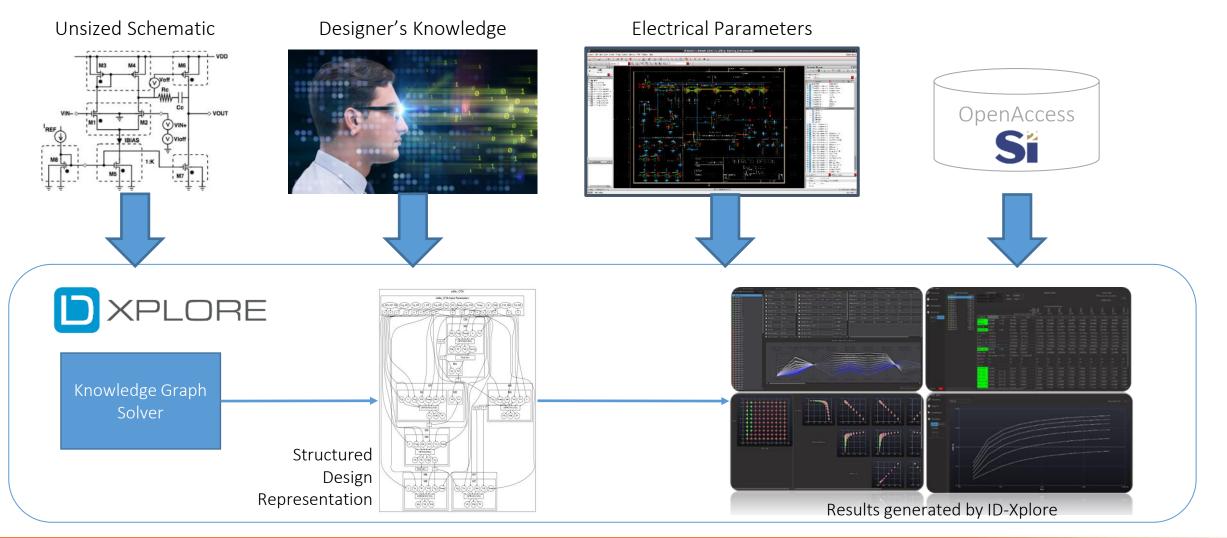

### ID-Xplore<sup>™</sup>

#### A Deterministic AI Knowledge Graph Solver for Analog Chip Design and Migration

#### Use Case: Sizing a 75-Devices Class AB RF-Amplifier

35 000,00 30 824 secs 180x Faster 30 000,00 25 000,00 20 000,00 15 000,00 10 000,00 5 000,00 Parallel Parallel with G-Xpress 0,00 **Parallel Partitions** Number of active cores Parallel Partitions with G-Xpress 170 secs

## Ultra Fast Design & Migration thanks to:

- Jacobian Free computations

- Graph-Based Model of Computation

- Graph-based Design Approach

- Intelligent Design Space Partitioning

- Intelligent Design Space Exploration

- Using multi-core and Compute Farm

- Very Fast Graph-Based PVT Analysis

### Analog Design Flow with ID-Xplore<sup>™</sup>

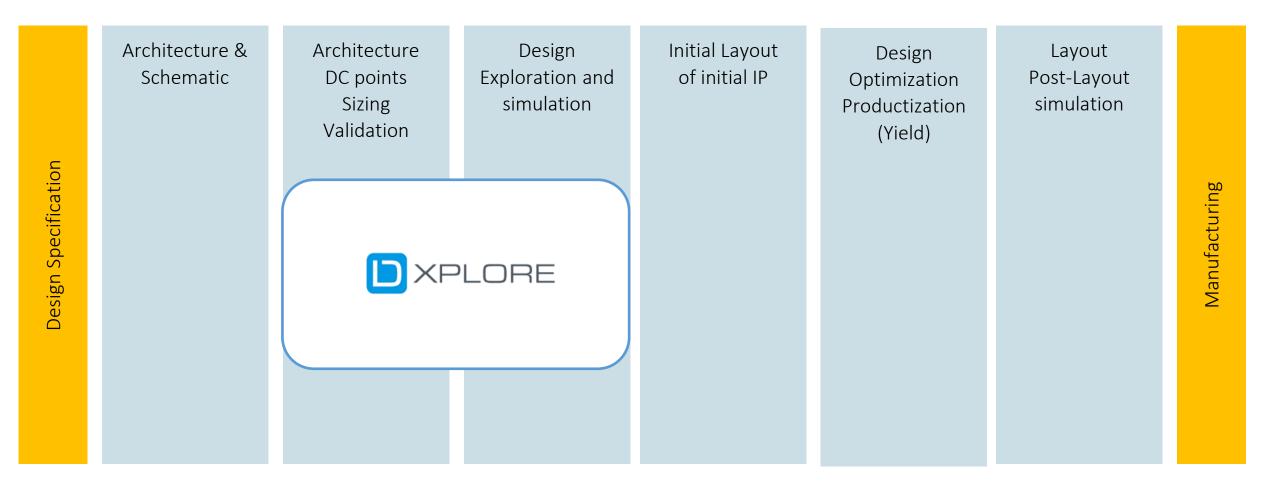

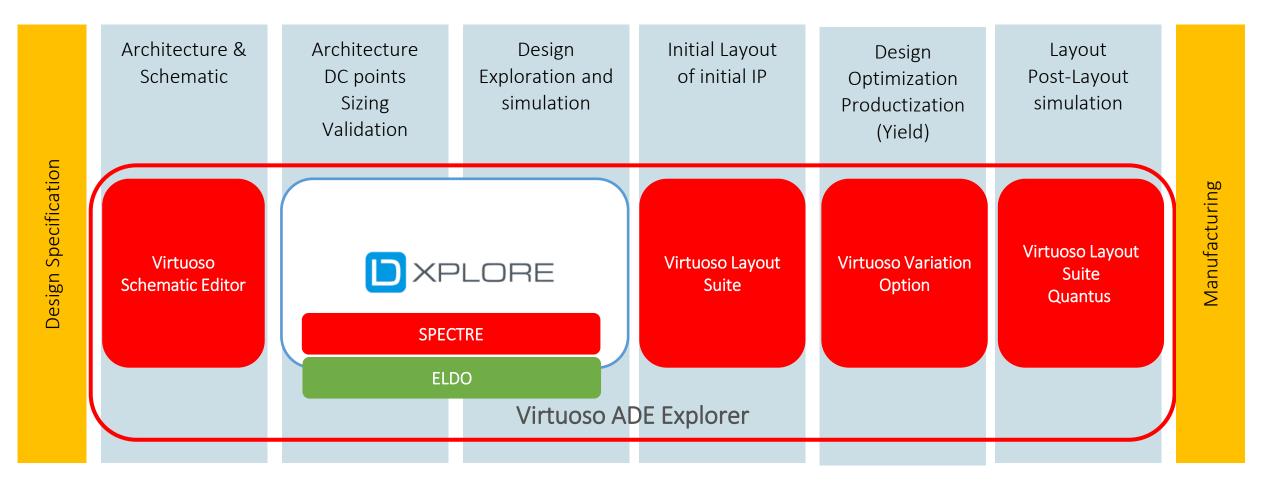

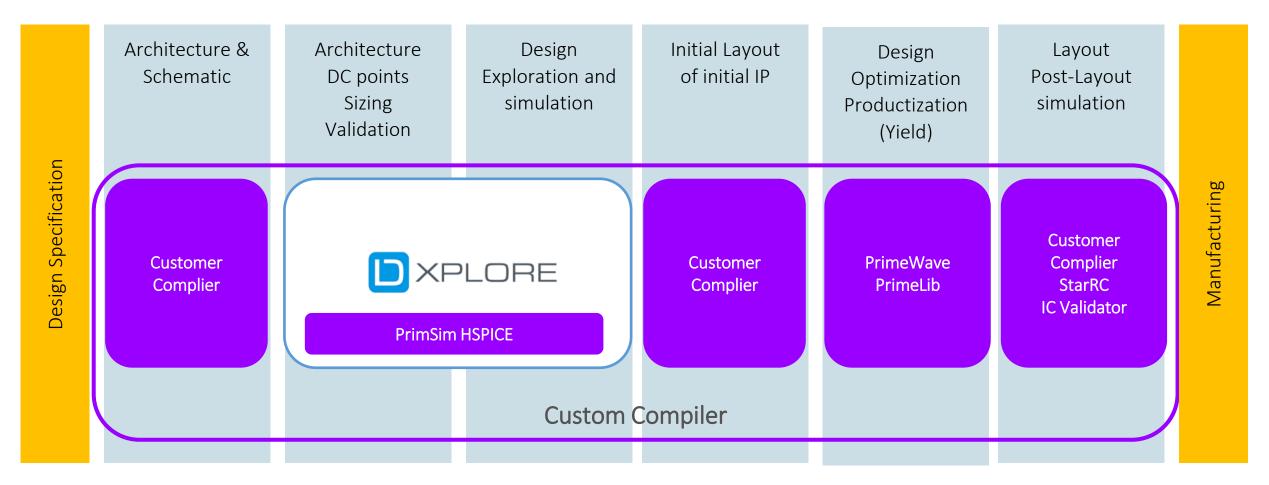

### Positioning ID-Xplore<sup>™</sup> in Analog Design Flow

### Positioning ID-Xplore<sup>™</sup> in Cadence Analog Design Flow

### Positioning ID-Xplore<sup>™</sup> in Synopsys Analog Design Flow

#### First Cognitive EDA for Design Exploration of Analog ICs

### Added Values for Analog IC

#### Customer

- Interactive top-down approach for analog designers (creativity + help Brainstorming ideas)

- Solution for tasks currently done outside computers

- Better use of analog experts time

- Quality focus & Start Validation upfront

- Efficient reuse & migration

- Build IP libraries

- High productivity gain

### EDA Partner

- Introduce top-Down methology in analog to gain and secure market share, based on top of existing products

- Differentiator with precise analog models

- Secure by patents

- Available products & team

- Important potential : RF, electrical checker, multi-domains, ...

- High potential revenue

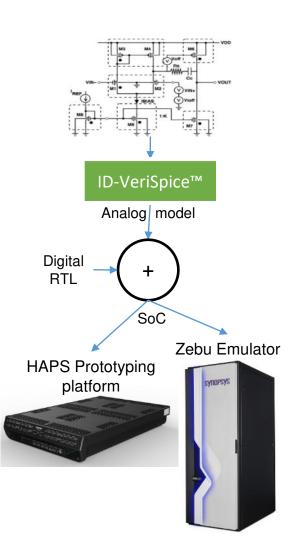

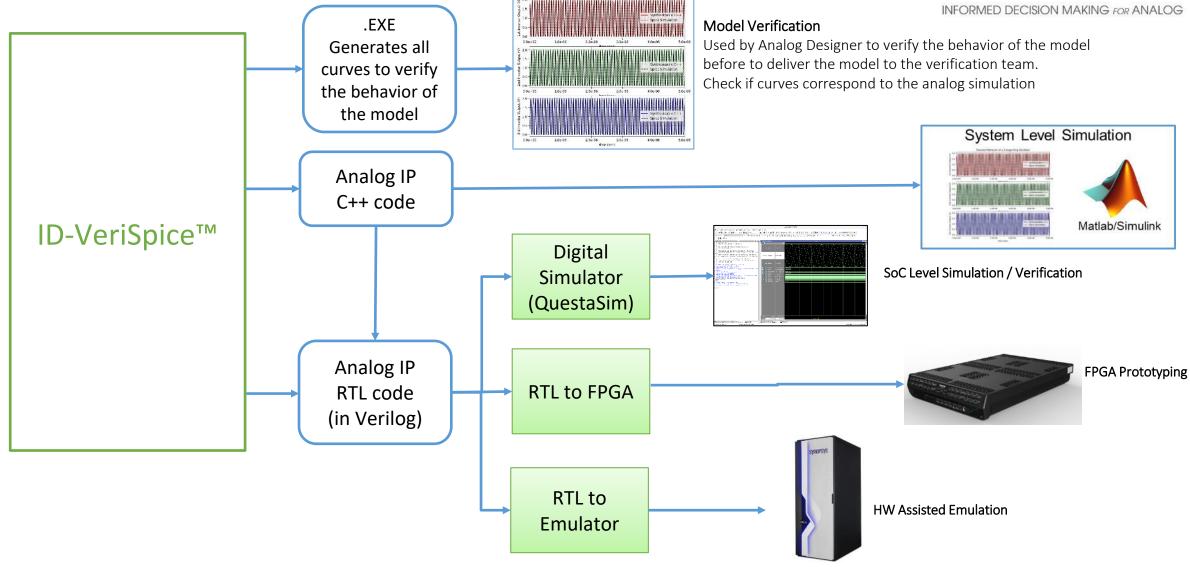

# **ID-VeriSpice**<sup>™</sup>

#### Automatic Generation of Real Number Models for Analog IP

### Why ID-VeriSpice<sup>™</sup>?

#### Concept:

Automatic conversion of a netlist/Schematic of an analog IP into a digital model with SPICE accuracy

#### Use Cases

- Verification and validation of a digital SoC surrounded by analog lps

- Simulating analog blocks in digital simulation environment with spice accuracy

- **Prototyping** of **SoC** and system including analog blocks (FPGA, HW-assisted system)

- System simulation for reliability & failure analysis (DFMEA/FMEA)

- Building comprehensive Digital Twin including analog IPs (PAVE 360, Twin Builder, ...)

- Transaction-Level modeling for Analog Ips

### **ID-VeriSpice™** Overview

Transient Behavior of a 3-stage Ring Oscillator

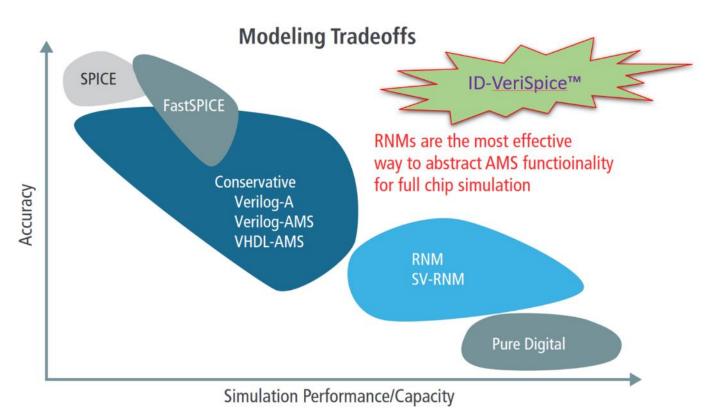

### AMS Verification State-Of-The-Art

Figure 2: Model accuracy versus performance gain for mixed-signal simulation.

#### Limitation of Current AMS Modelling!

- Manual modelling in RNM

- No automation available

- Difficult to reach Spice accuracy

- Modelling depends on design expertise

ID-VeriSpice<sup>™</sup> brings both Accuracy and Scalability

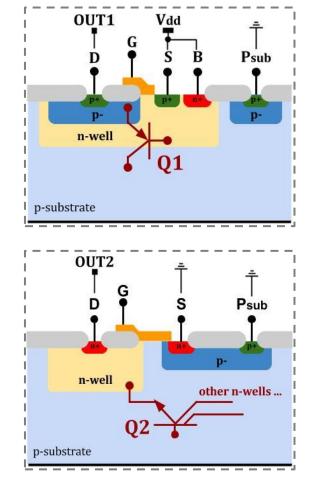

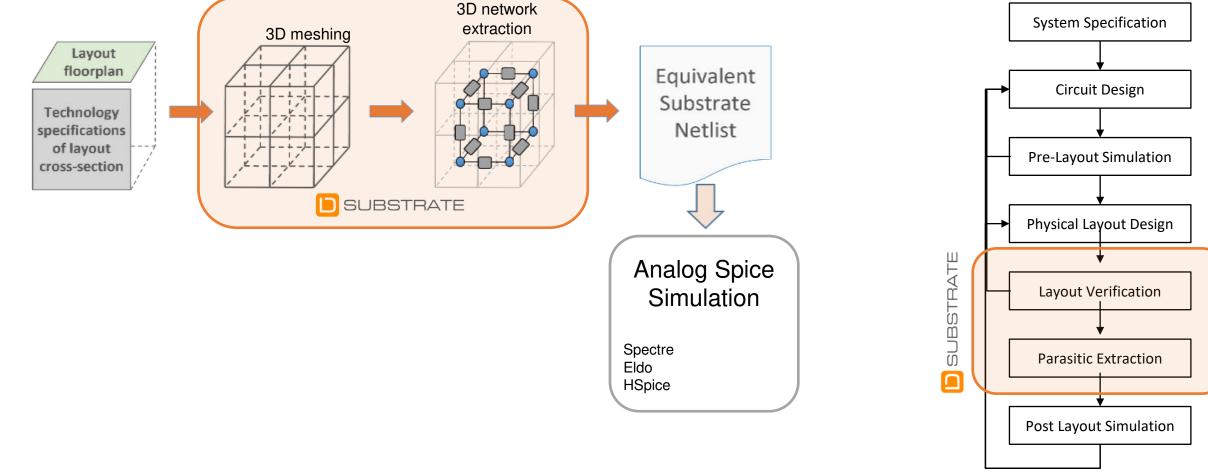

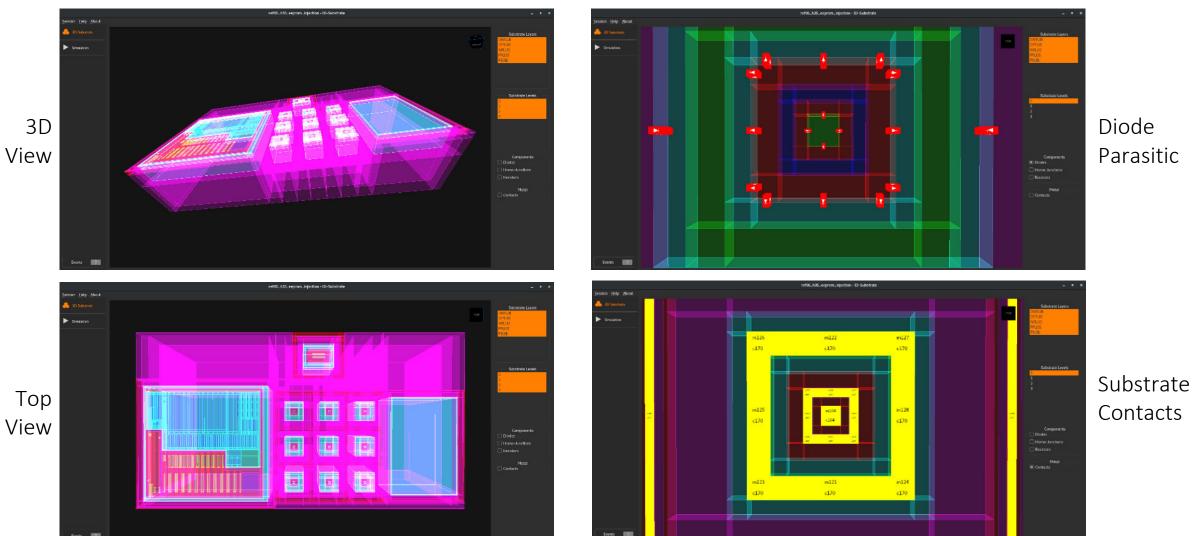

# **ID-Substrate<sup>™</sup> for Reliability**

Verification and Signoff tool to ensure reliability and Robustness before tape-out

ID-Substrate was developed to **predict and prevent substrate failures** quickly and accurately before the silicon fabrication

- **Minority carrier injection** and **lateral propagation** in substrate are difficult to model since they depend on layout distances.

- Existing SPICE simulators ignore the impact of these effects as they do **not look inside the substrate**.

- Substrate failures can therefore only be detected during lab tests after silicon is already fabricated and cause circuit redesign

- 40% of substrate failures are due to minority carrier propagation.

### **ID-Substrate<sup>™</sup> Value Proposition**

INTENTO DESIGN

- Propose a modeling and simulation methodology for systematic prediction and prevention of substrate coupling effects and latch-up due to minority and majority carriers.

- Model multiple emitter/multiple collector lateral bipolars.

- Simulate complex substrate phenomena leading to latch-up conditions

- Simulate minority carrier propagation in DC, AC & TRAN.

- CAD Framework on top of OpenAccess Standard.

- A TCAD-Like behavioral substrate simulation for full chip

A fast sign-off verification tool to capture and analyze all types of substrate noise coupling with high precision

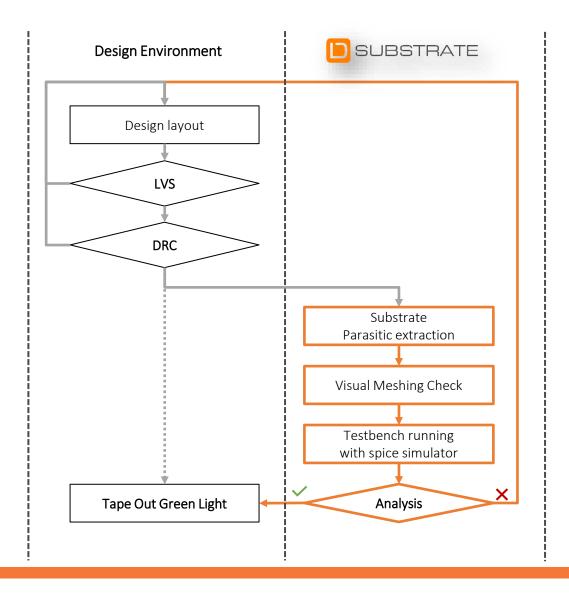

**Design Flow**

#### **ID-Substrate<sup>™</sup> Flow**

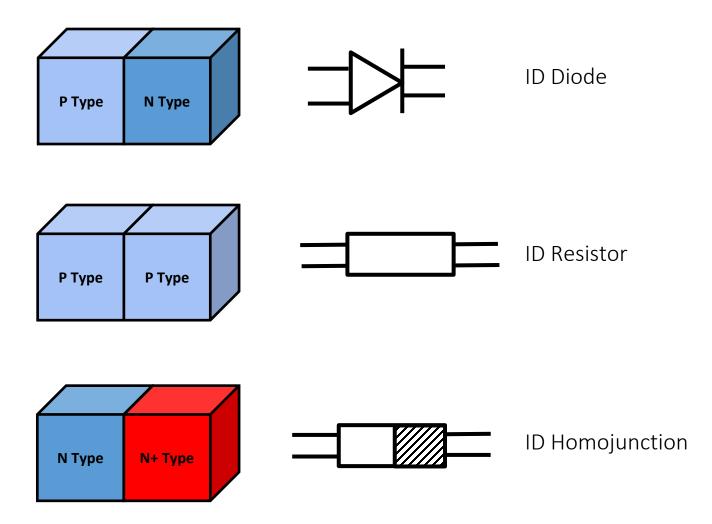

#### **ID-Substrate<sup>™</sup> Models**

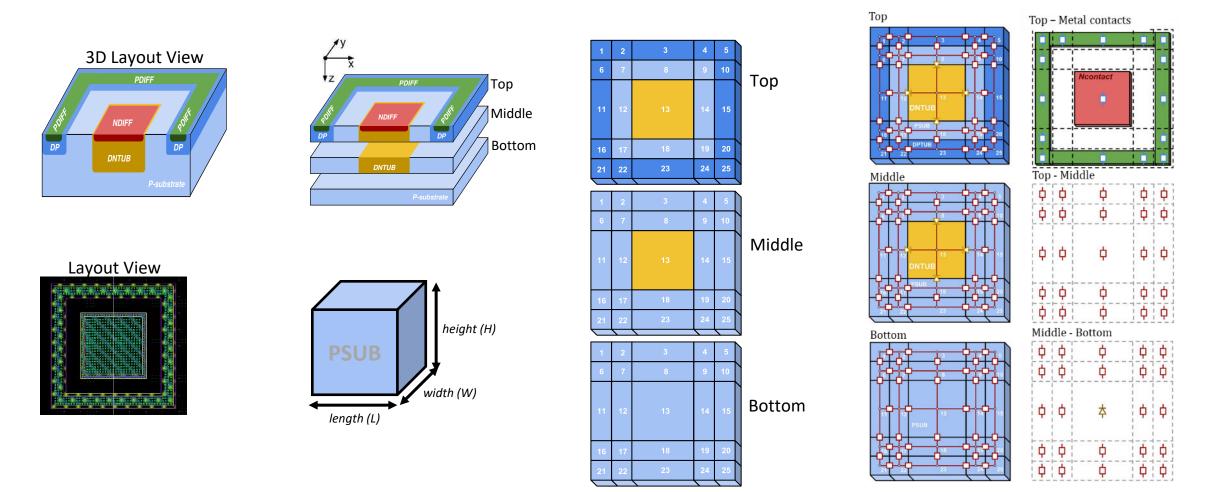

#### Meshing Strategy Example with N-Well Diode in PSUB

3D Substrate Network

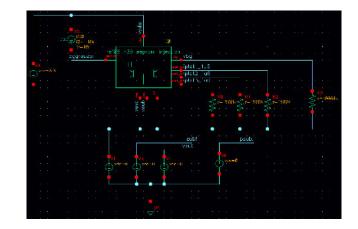

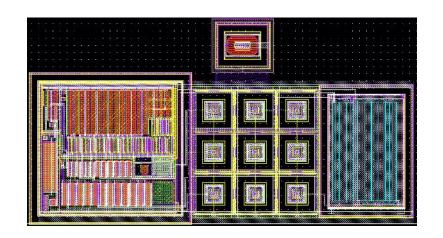

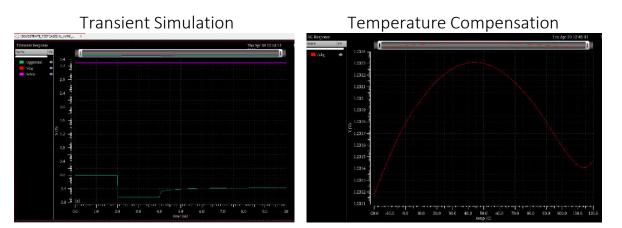

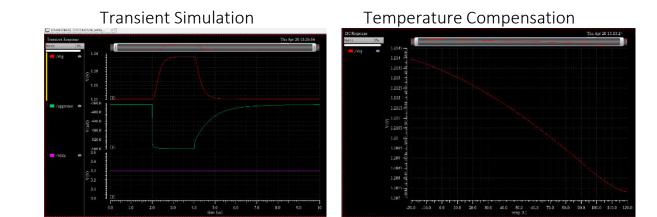

### Substrate Coupling Detection BandGap Simulation on AMS 0.35µm HV for Automotive

Without ID-Substrate Parasitic

#### With ID-Substrate Parasitic

# 3D-Viewer for Substrate Parasitic (under development)

Intento Design Confidential Information

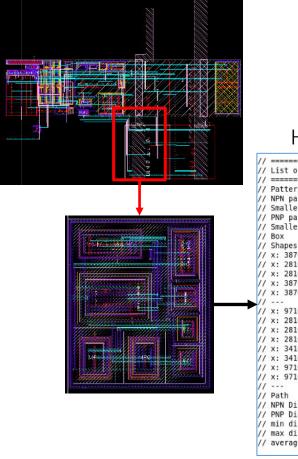

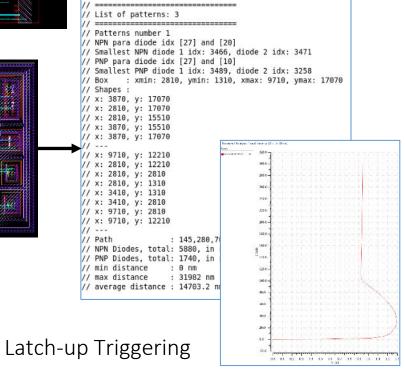

### Static Identification of Latch-up Hotspots No Simulation

#### Problem to solve:

Microcontroller with 2M devices with Latch-up issue.

Simulation for full chip not possible.

| // =========                           | ======= | ========                              |               |               |       |

|----------------------------------------|---------|---------------------------------------|---------------|---------------|-------|

| // List of patt                        |         |                                       |               |               |       |

| // =================================== |         |                                       |               |               |       |

| // NPN para did                        |         | [514] 200                             | 1 [510]       |               |       |

| // Smallest NPN                        |         |                                       |               | idy, 70074    |       |

| // PNP para did                        |         |                                       |               | 10X: 70974    |       |

| // Smallest PNP                        |         |                                       |               | idv · 69424   |       |

| // Box : xmi                           |         |                                       |               |               | 76170 |

| // Shapes :                            |         | , , , , , , , , , , , , , , , , , , , | 20070, Allax. | Hosto, Jindxi | /01/0 |

| // x: 35875, y:                        | 25470   |                                       |               |               |       |

| // x: 34690, y:                        |         |                                       |               |               |       |

| // x: 34690, y:                        |         |                                       |               |               |       |

| // x: 35875, y:                        |         |                                       |               |               |       |

| // x: 35875, y:                        |         |                                       |               |               |       |

| //                                     |         |                                       |               |               |       |

| // x: 40940, y:                        | 76170   |                                       |               |               |       |

| // x: 34690, y:                        | 76170   |                                       |               |               |       |

| // x: 34690, y:                        | 63780   |                                       |               |               |       |

| // x: 35875, y:                        | 63780   |                                       |               |               |       |

| // x: 35875, y:                        |         |                                       |               |               |       |

| // x: 40340, y:                        |         |                                       |               |               |       |

| // x: 40340, y:                        |         |                                       |               |               |       |

| // x: 40940, y:                        |         |                                       |               |               |       |

| // x: 40940, y:                        | 76170   |                                       |               |               |       |

| //                                     |         |                                       |               |               |       |

| // Path                                |         | 2505,1523                             |               |               |       |

| // NPN Diodes,                         |         |                                       |               |               |       |

| // PNP Diodes,                         |         |                                       | range: all    |               |       |

| // min distance                        |         |                                       |               |               |       |

| <pre>// max distance</pre>             |         | 57939 nm                              |               |               |       |

| <pre>// average dist</pre>             | ance :  | 31986.8 1                             | nm            |               |       |

#### Hotspot Identification

#### Intento Design – Main Office

10 Rue de Richelieu 75001 Paris, France Phone: +33 9 72 63 27 40

Website: <a href="http://www.intento-design.com">www.intento-design.com</a>

E-mail: info@intento-design.com

Intento Design – Grenoble Office 25 rue Pierre Semard 38000 Grenoble, France

> ID-Xplore, ID-Substrate and Intento Design logo are trademarks or registered trademarks of Intento Design in various countries. All trademarks, service marks, and trade names are the marks of the respective owner(s), and any unauthorized use thereof is strictly prohibited. All terms and prices are indicative and subject to any modification without notice.